## High-Level Synthesis of Neural Networks for FPGAs

Christof Schlaak - Christophe Dubach

## All you need is Neural Networks

- For classification, prediction or clustering tasks

- CHALLENGES

- 1) High computing needs & inherently parallel → How can we accelerate NNs?

- 2) Many different NN models

- 3) Implementations evolve often and regularly

## All you need is FPGAs

- Highly efficient (better than CPU/GPU)!

- Reconfigurable (better than ASIC) → exploit different NN types & adapt to NN changes!

- CHALLENGES

- 1) Designed in low-level HDL error-prone and time-consuming

- 2) Require HW design expertise

- 3) Portability?

DSE

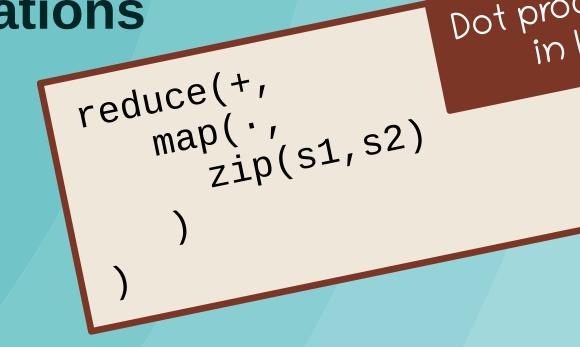

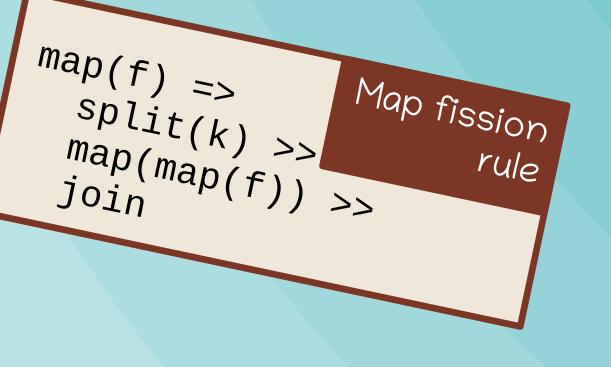

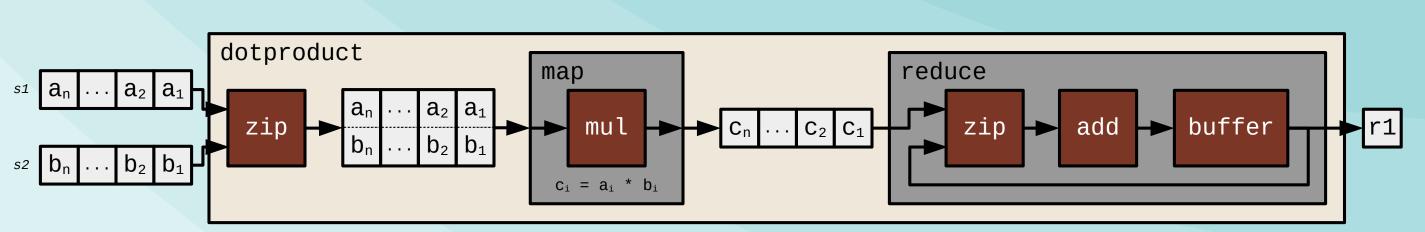

- LIFT is a high-level functional, data-parallel language

- LIFT offers performance-portability

- LIFT generates optimised hardware implementations

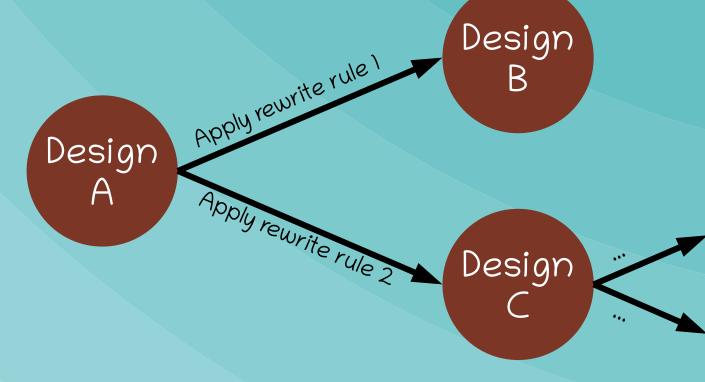

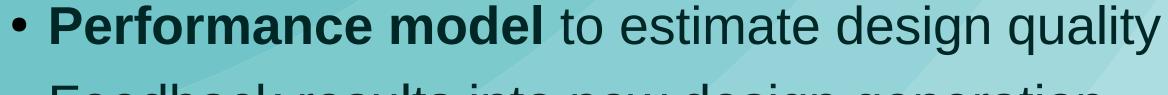

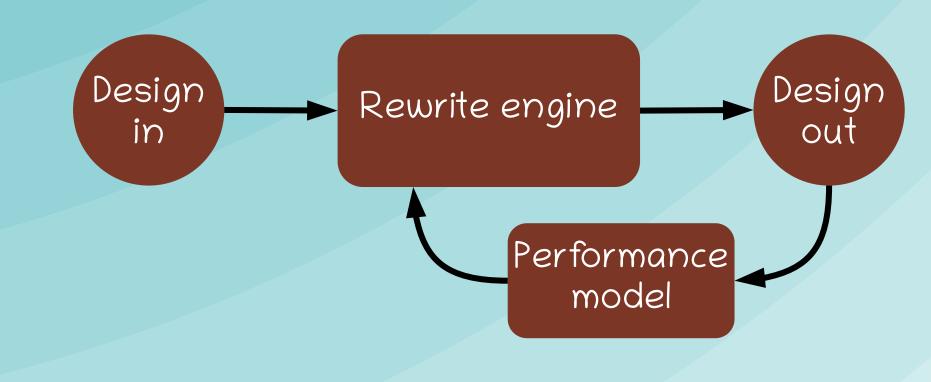

ML can be used to make the best rule choices

HDL

out

- Feedback results into new design generation

- Generated design is precisely predictable

- very accurate estimations!

- Each functional expression implies a specific hardware design → straightforward HDL generation

- No need for intermediate software-like representation

- Support arbitrary NN architectures and tools (e.g. TF) through ONNX

- Support RNNs in future by adding further primitives (e.g. fold, mapAccum)